近期,,中國科學(xué)技術(shù)大學(xué)在硬件高斯隨機數(shù)生成算法的研究中取得重要進展,,提出了一種新式的硬件高斯隨機數(shù)生成器設(shè)計方法,。該成果近日以“Flexible FPGA Gaussian Random Number Generators With Reconfigurable Variance”為題在線發(fā)表于電子工程領(lǐng)域知名期刊《IEEE Transactions on Circuits and Systems I: Regular Papers》,。中國科大博士研究生陳卓為第一作者,;中國科大宋克柱教授為通迅作者,。

加性高斯白噪聲(Additive white Gaussian noise, AWGN)模型通常被用來反映多種噪聲共同作用的疊加結(jié)果,因此高斯隨機數(shù)(Gaussian random number, GRN)生成器,,作為一種能夠為生成加性高斯白噪聲的硬件模塊,,是許多高性能硬件仿真系統(tǒng)中的重要部件,在通信系統(tǒng)仿真,、金融仿真等場景下均有著重要作用,。高斯隨機數(shù)反映的是被仿真系統(tǒng)的隨機性,而這一隨機性通常是一些重要系統(tǒng)特征,,例如SerDes系統(tǒng)中的誤碼,,的形成原因。因此,,高斯隨機數(shù)生成器的統(tǒng)計學(xué)準確度會直接影響仿真結(jié)果的可靠性,,高斯隨機數(shù)生成器也是此類系統(tǒng)中的重要組成部件。

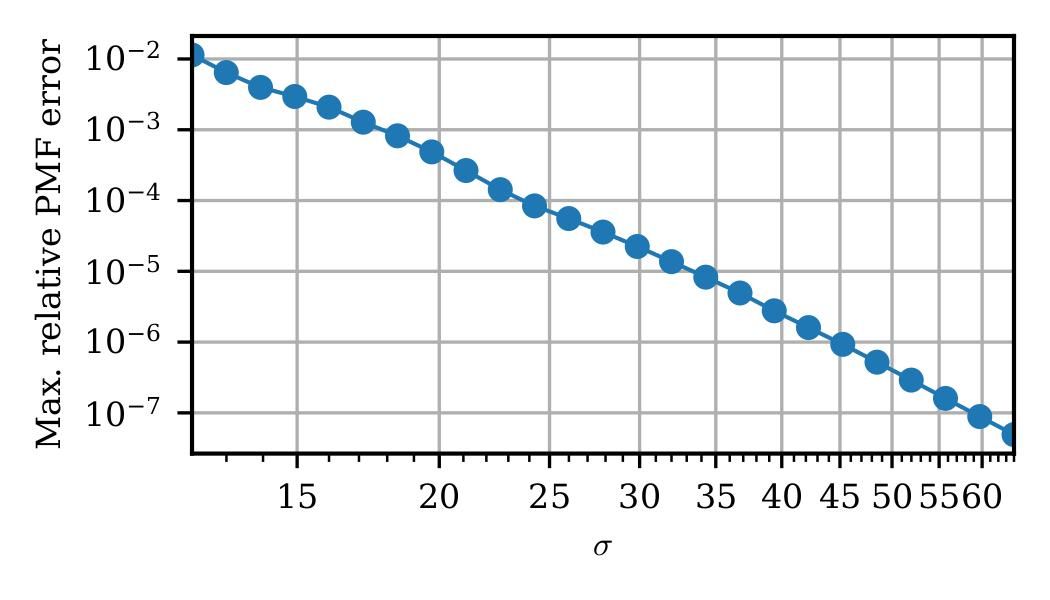

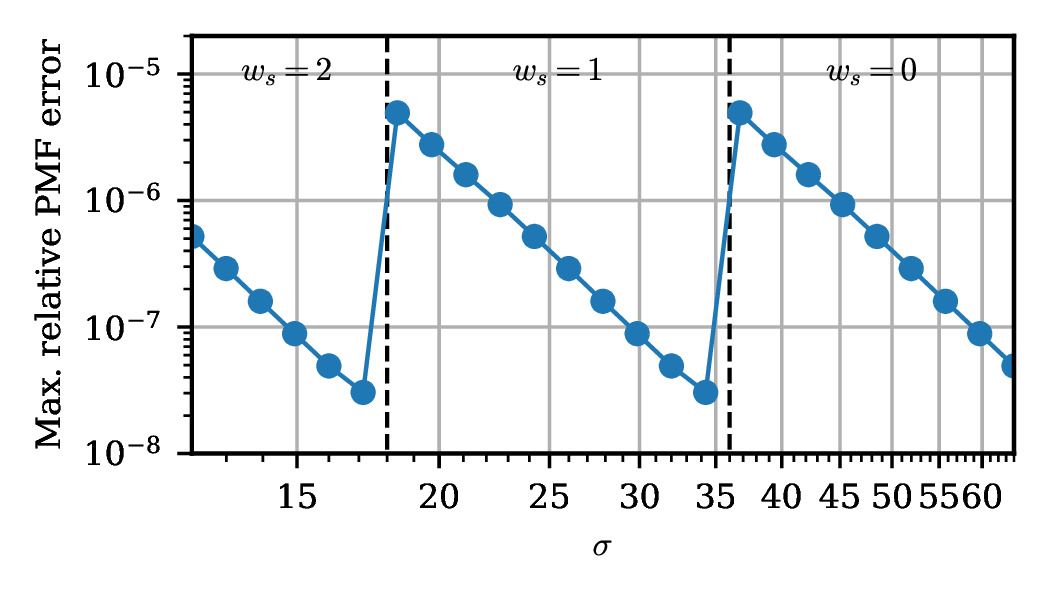

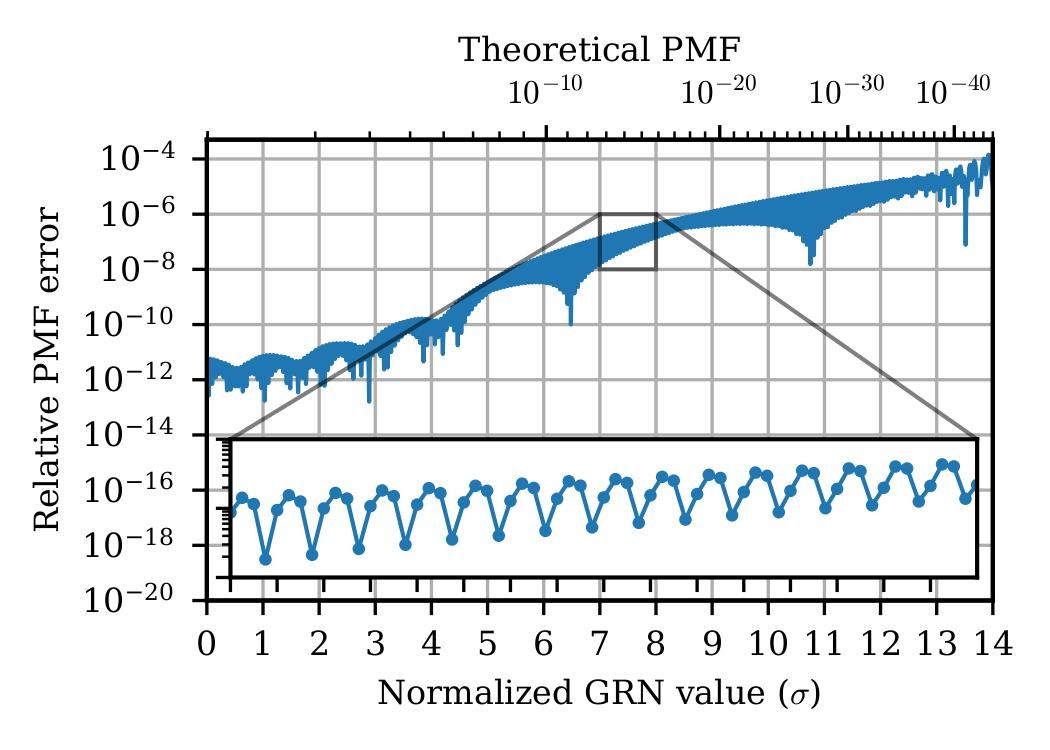

自從2000年工程師們嘗試用硬件實現(xiàn)了Box-Muller算法后,,關(guān)于硬件高斯隨機數(shù)生成算法的研究就層出不窮,。傳統(tǒng)的適用于硬件的高斯隨機數(shù)生成算法,包括Ziggurat法,、Box-Muller法,、Inversion法等,通常只針對σ=1的標準高斯分布,,在硬件系統(tǒng)中使用時需要使用額外的乘法器和取整器,,從而引入額外的硬件消耗和誤差來源。此外,,由傳統(tǒng)方法設(shè)計的高斯隨機數(shù)生成器的輸出范圍往往只能在參數(shù)設(shè)計完成后通過測試或理論分析得到,,提高輸出范圍的方法不夠直接。研究團隊以一種相對較新的Piecewise-CLT算法作為基礎(chǔ),,在對算法解析式的推導(dǎo)過程中,,通過引入可變的σ值和預(yù)先確定的高斯隨機數(shù)輸出范圍,獲得了針對任意σ值和任意輸出范圍的高斯隨機數(shù)生成器的設(shè)計方法,,并以此設(shè)計出了理論輸出范圍達到±14σ的生成器(圖1),。在嘗試為算法引入可重配置性時,研究團隊發(fā)現(xiàn),,如果直接重配置已有硬件架構(gòu)的σ值,,生成器的誤差將隨著σ值的降低而不斷升高(圖2),,使其實用性大大降低。為了解決這一問題,,該團隊為算法引入名為縮放因子(scaling index)的參數(shù),,使得算法在針對不同σ值進行隨機數(shù)生成時,會根據(jù)縮放因子的不同對相關(guān)數(shù)值進行縮放,,從而得到相對穩(wěn)定的誤差曲線(圖3),,從而使得σ值的實時配置真正成為可能。

圖 1 理論輸出范圍達到±14σ的生成器的相對概率誤差與隨機數(shù)大小的關(guān)系

圖 2 未引入縮放因子時的誤差曲線

圖 3 引入縮放因子后的誤差曲線

基于上述研究,,研究團隊提出了提出一種新式的硬件高斯隨機數(shù)生成器設(shè)計方法,。相較于傳統(tǒng)的硬件高斯隨機數(shù)生成器設(shè)計方法,該方法由于其支持任意σ值,、任意輸出范圍,、可重配置的優(yōu)點,具有更大的靈活性和使用性,,為設(shè)計高時鐘速率,、高并行度、高硬件資源利用率的高性能硬件仿真系統(tǒng)提供有力支持,。

該項研究工作得到了國家重點研發(fā)計劃項目的支持,。

論文鏈接:https://ieeexplore.ieee.org/document/10477259

(物理學(xué)院、核探測與核電子學(xué)國家重點實驗室,、科研部)